인텔, 차세대 CPU 생산 일정 내년 하반기 연기TSMC, 3나노 생산 확장 계획 차질 불가피삼성, GAA 기반 기술 공개… 고객사 확대 기대

-

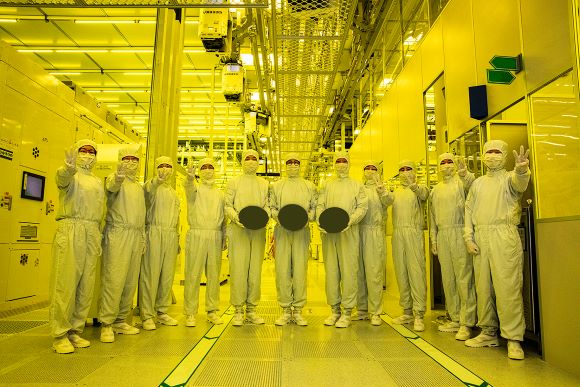

- ▲ ⓒ삼성전자

글로벌 파운드리 1위 대만 TSMC의 3나노 생산 계획에 차질이 빚어질 것이라는 전망이 나온다. TSMC에 앞서 선제적으로 3나노 공정 양산에 돌입한 삼성전자가 파운드리 시장에서 추격의 발판을 만들 수 있을지 이목이 집중된다.9일 관련업게에 따르면 최근 TSMC가 3나노 양산을 위한 생산시설 확장 계획에 차질을 빚을 수 있다는 전망이 나온다.TSMC의 주요 고객사인 인텔이 차세대 CPU '메테오 레이크(Meteor Lake)'의 생산 일정을 내년 하반기 이후로 연기했다는 관측 때문이다. 이에 대만 시장조사기관인 트렌드포스는 TSMC 생산 계획에도 영향이 미칠 수 밖에 없다고 내다봤다.인텔은 14세대 CPU 메테오레이크를 TSMC의 3나노 공정으로 제작하는 방안을 검토했지만 오는 2024년부터 자체적으로 2나노 양산을 시작하겠다고 발표한 만큼 TSMC의 3나노를 활용하지 않을 가능성도 제기되고 있다. 다만 애플은 기존 계획대로 2023년 아이폰15에 탑재될 ‘A17바이오닉’과 M시리즈 등에 TSMC의 3나노 공정을 활용할 것으로 전망이다.때문에 TSMC의 3나노 양산 시점도 내년 초로 예상된다. 당초 올 상반기일 것으로 예상됐지만 하반기로 연기됐고 또 다시 내년 상반기까지 밀린 것으로 예상된다.이에 따라 TSMC보다 한 발 앞서 양산에 나선 삼성전자가 기술 주도권을 선점할 수 있을지 이목이 집중되고 있다.삼성전자는 지난 6월 세계 최초로 GAA(Gate-All-Around) 기술을 적용한 3나노(nm, 나노미터) 파운드리 공정 기반의 초도 양산을 시작했다.삼성전자는 이번에 반도체를 구성하는 트랜지스터에서 전류가 흐르는 채널(Channel) 4개면을 게이트(Gate)가 둘러 싸는 형태인 차세대 GAA 기술을 세계 최초로 적용했다. 채널의 3개면을 감싸는 기존 핀펫 구조와 비교해 GAA 기술은 게이트의 면적이 넓어지며 공정 미세화에 따른 트랜지스터 성능 저하를 극복하고 데이터 처리 속도와 전력 효율을 높이는 차세대 반도체 핵심 기술로 손꼽힌다.또한 삼성전자는 채널을 얇고 넓은 모양의 나노시트(Nanosheet) 형태로 구현한 독자적 MBCFET GAA 구조도 적용했다.나노시트의 폭을 조정하면서 채널의 크기도 다양하게 변경할 수 있으며, 기존 핀펫 구조나 일반적인 나노와이어(Nanowire) GAA 구조에 비해 전류를 더 세밀하게 조절할 수 있어 고성능·저전력 반도체 설계에 큰 장점이 있다.삼성전자는 나노시트 GAA 구조 적용과 함께 3나노 설계 공정 기술 공동 최적화(DTCO, Design Technology Co-Optimization)를 통해 PPA(Power:소비전력, Performance:성능, Area:면적)를 극대화했다.삼성전자는 앞으로 고객 요구에 최적화된 PPA, 극대화된 전성비(단위 전력당 성능)를 제공하며, 차세대 파운드리 서비스 시장을 주도해 나갈 계획이다.시장조사업체 트렌드포스에 따르면 올해 1분기 파운드리 매출 점유율은 TSMC가 53.6%로 1위를 기록하는 가운데 삼성전자는 16.3%에 그쳤다. GAA 기술 기반 3나노 반도체에 고성능 제품을 원하는 고객사의 주문이 몰리면 삼성전자의 점유율은 더 확대될 것으로 전망된다. TSMC의 3나노 양산 시점이 늦어지고 GAA 기술을 적용한 삼성전자 반도체와 성능에 차이가 있을 것으로 예상되는 만큼 삼성전자의 추격도 가능하다는 게 업계 시각이다.