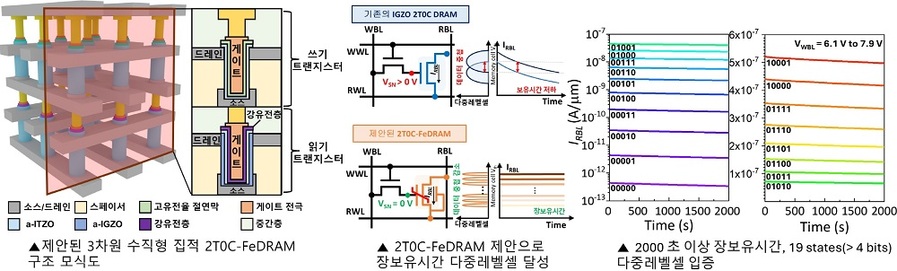

4-bits 다중레벨셀 2000초 보유시간 달성고집적 저전력소모 D램으로 발전 가능성 제시

-

- ▲ 한양대 김영현 교수(책임 교신저자·왼쪽)와 한양대 노태현 연구원(제1저자).ⓒ한양대

한양대학교는 ERICA캠퍼스 나노광전자학과 김영현 교수 연구팀이 초장보유시간과 다중레벨셀 구현이 가능한 차세대 D램 기술을 개발했다고 20일 밝혔다.이번 연구는 산화물반도체와 강유전체를 기반으로 한 고집적·초저전력 3차원 D램 기술의 잠재적 응용 가능성을 제시한다. 산화물 반도체는 산소와 여러 물질이 결합된 차세대 반도체 물질, 강유전체는 외부 전기장에 의해 자발적으로 분극이 발생하고, 전기장이 제거된 후에도 분극이 유지되는 성질을 가진 물질을 뜻한다.현재 D램은 1개의 트랜지스터와 1개의 커패시터로 구성돼 저전력 소모와 고집적 소자의 개발이 이뤄지고 있다. 그러나 고용량의 커패시터를 위해선 커패시터의 높이를 늘려야 한다. 극한의 미세화 공정에서는 공정 난도가 증가하며 누설전류로 인해 데이터 보유시간이 짧아지는 문제가 있다. 이는 전력 소모를 증가시키는 요인이다.이런 문제를 해결하기 위해 저누설전류 특성을 가진 산화물 반도체를 활용한 2T0C DRAM이 연구되고 있지만, 데이터를 저장할 때 전하 누설전류에 의해 보유시간이 제한되는 문제가 있었다. 또한 산화물 반도체의 문턱전압 이동과 신뢰도 저하로 인해 D램의 비트라인 전류가 감소하고, 다중레벨셀 구현이 어려운 단점이 있었다. -

- ▲ 강유전성 트랜지스터를 이용한 장보유시간 다중레벨셀 2T0C-FeDRAM 제안 및 모식도 / 새로운 동작과 측정 방식으로 우수한 특성을 입증했다.ⓒ한양대

연구팀은 이를 극복하기 위해 자발 분극이 항상 존재하는 강유전체를 읽기 트랜지스터의 절연층으로 사용하고, 데이터를 분극 형태로 저장해 누설전류를 최소화할 수 있는, 이른바 2T0C-FeDRAM 기술을 개발했다. 또한 다중층 산화물 반도체 채널을 최적화해 신뢰성과 보유시간을 증가시키고, 낮은 공정 온도로 3D 집적 공정을 가능하게 했다.연구 결과, 전기적으로 연결된 강유전체 박막트랜지스터와 산화물 반도체 트랜지스터로 구성된 2T0C-FeDRAM이 4비트 다중레벨셀에서 2000초 이상의 보유시간을 구현했다. 이는 저전력 소모와 고밀도 3D 집적 D램 소자의 발전 가능성을 의미한다. 인공지능(AI) 반도체용 학습과 추론에 사용되는 D램 기반의 PIM(Processing-in-Memory)용 고대역폭 메모리(HBM)의 소비전력을 획기적으로 낮출 것으로 기대된다.김 교수는 "이번 연구는 저전력, 고용량 3D D램 애플리케이션을 위한 2T0C-FeDRAM 비트셀의 타당성을 입증한 성과"라며 "산업체와 협력해 연구 결과를 차세대 메모리 기술에 적용함으로써 AI 반도체 패권 경쟁에서 우위를 확보하고, 국가 기술 발전에 이바지하겠다"고 말했다.이번 연구논문(First demonstration of 2T0C-FeDRAM: a-ITZO FET and double gate a-ITZO/a-IGZO FeFET with record-long multibit retention time of > 4-bit and > 2000s)은 영국 왕립화학회의 나노스케일 분야 SCI-E 학술지인 'Nanoscale' 8월호에 실렸다. 김 교수가 교신저자, 한양대 ERICA 나노광전자학과 노태현 연구원(석사과정)이 제1저자로 참여했다. 한국과학기술연구원(KIST) 안대환 선임연구원, 한양대 안지훈·김재균 교수가 공동 참여했다.