기존 CMOS 공정 기반의 고집적·저전력 반도체 구현 위한 대안 제시소재 분야 세계적 학술지 '어드밴스드 펑셔널 머티리얼즈'에 지난달 게재

-

- ▲ 정재경 교수.ⓒ한양대

한양대학교는 융합전자공학부 정재경 교수팀이 기존 CMOS 반도체 공정 기술을 기반으로 하는 '수직 집적이 가능한 삼진 로직 소자 기술'을 개발했다고 4일 밝혔다.기존 실리콘 기반 반도체는 무어의 법칙에 따라 집적도를 높이는 방식으로 성능을 향상해 왔다. 그러나 배선 간 간격 축소에 따른 기생 저항과 커패시턴스 증가로 성능 저하와 전력 소모 문제에 직면하고 있다. 이를 해결할 새로운 패러다임으로, '0'과 '1' 두 개의 논리 상태를 갖는 이진 로직을 넘어 세 개(0, 1, 2)의 상태를 동시에 처리할 수 있는 '삼진 로직' 기술이 주목받고 있다.삼진 로직을 구현하려면 기존 트랜지스터와 달리 특이 전도 특성인 음미분전도(NDT)를 갖는 트랜지스터가 필요하다. 하지만 기존 NDT 트랜지스터는 CMOS 공정과의 호환성과 대면적 집적에 한계가 있었다. -

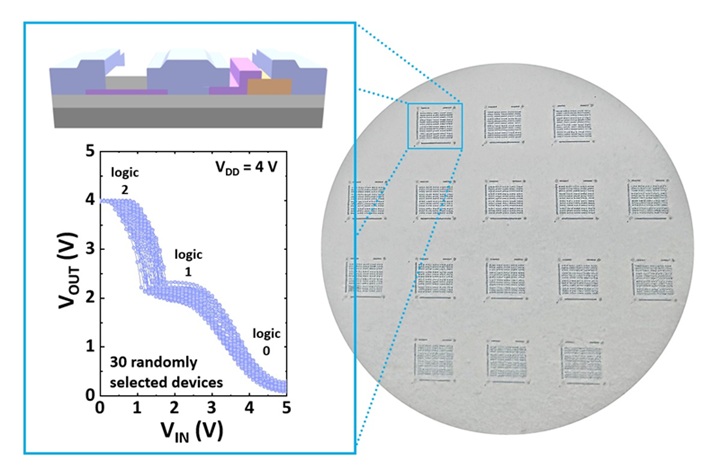

- ▲ 개발된 삼진 로직 구조도. 웨이퍼 스케일로 제작된 텔루륨(TeO)과 인듐갈륨주석(InGaSnO) 산화물 기반 삼진 인버터 소자.ⓒ한양대

이런 한계를 극복하기 위해 연구팀은 CMOS 공정 중 하나인 스퍼터링(Sputtering)을 활용하고, 저온 공정에 적합한 고성능 p채널 산화물 '텔루륨 산화물(TeOx)'과 n채널 산화물 '인듐갈륨주석산화물(IGTO)'을 적용했다. 이를 통해 NDT 특성을 갖는 이종접합 트랜지스터 기반의 삼진 인버터 소자 구현 기술을 제안했다. 또한 인버터 구조를 최적화해 세 개의 명확한 논리 상태를 구현하고, 웨이퍼 스케일 제작을 통해 대면적 집적화 가능성도 확인했다.정 교수는 "이번 연구는 기존 다치 로직에서 한계로 여겨졌던 고집적화 문제를 해결할 가능성을 제시한 것"이라며 "새로운 반도체 패러다임의 상용화에 기여할 수 있다"고 말했다.이번 연구 결과는 소재 분야의 세계적 학술지인 '첨단 기능성 소재(Advanced Functional Materials)'에 지난달 19일 온라인 게재됐다. 한양대 정재경, 성명모 교수, 미국 스탠퍼드대 김태규 박사후연구원이 공동 교신저자, 한양대 디스플레이융합공학과 정찬우 석박사통합과정생과 SK하이닉스 이준호 석사연구원이 공동 제1저자로 각각 참여했다.이번 연구는 과학기술정보통신부 산하 한국연구재단의 나노 및 소재기술개발사업, 혁신연구센터사업의 지원을 받아 수행됐다. -

- ▲ ⓒ한양대