고적층으로 갈수록 전력·열·인터페이스 부담 ↑ … 검증·양산 시간 늘어삼성, 메모리·파운드리·패키징·설계 '공동 최적화'로 병목 줄이는 전략SK, 공정 모듈화·다세대 재사용 '테크 플랫폼'·R&D AI로 개발 주기 방어

-

- ▲ ⓒ뉴데일리

AI(인공지능) 가속기 세대가 바뀔수록 HBM(고대역폭메모리)은 더 빠르고, 더 높게 쌓아야 한다. 하지만 스펙을 올릴수록 전력·열·인터페이스 부담이 커지고, 이를 풀기 위한 공정·패키징·설계 변경이 늘면서 검증과 양산까지 걸리는 시간이 길어지는 구조가 뚜렷해졌다는 게 업계 공통 인식이다. 이를 개선하기 위해 삼성전자와 SK하이닉스가 공통으로 꺼낸 키워드는 “제때 내놓는 능력”이었다.송재혁 삼성전자 디바이스솔루션(DS)부문 최고기술책임자(CTO)는 지난 11일 ‘세미콘 코리아 2026’ 기조연설 무대에서 메모리·파운드리·첨단 패키징을 모두 갖춘 구조가 AI가 요구하는 제품을 만드는 데 유리하다고 강조했다.이성훈 SK하이닉스 부사장도 같은 행사에서 “타이트 마켓에서 제때 좋은 제품을 출시할 수 있는 것이 메모리 경쟁력”이라며 케이던스(개발 주기)를 지키는 문제를 전면에 올렸다.◇삼성, 디바이스·패키지·설계 최적화 … 열·전력 병목을 ‘시스템’에서 줄인다삼성의 접근은 단일 칩 성능을 넘어 ‘시스템 단위’에서 병목을 줄이겠다는 것이다. 메모리·파운드리·첨단 패키징·설계를 함께 조정하는 공동 최적화(co-optimization)를 전면에 내세웠다. 종합반도체기업(IDM) 구조를 AI 시대 제품화에 유리한 조건으로 해석한 것이다.송 CTO는 차세대 적층 환경에서 하이브리드 본딩(하이브리드 카퍼 본딩 등) 준비하고 있다고 밝히면서, 관련 구조를 적용해 동작시킨 결과 열저항을 20% 이상 낮추고 베이스 다이 온도를 약 11% 줄였다고 밝혔다.삼성은 이 같은 접근을 통해 HBM 고도화 과정에서 커지는 발열·전력 부담을 낮추고, 설계·패키지 단계에서 병목을 줄이는 방식으로 제품화 시간을 관리하겠다는 구상이다. -

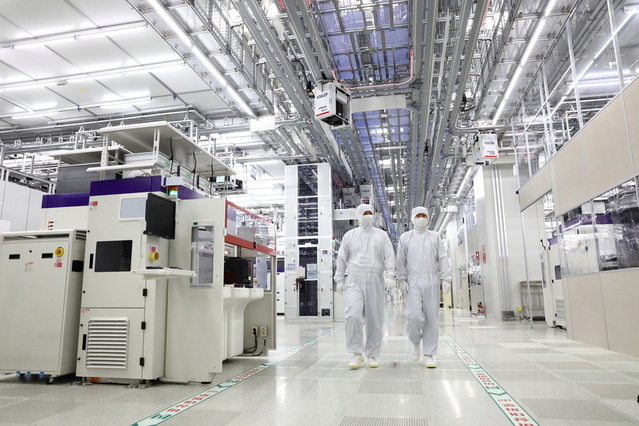

- ▲ 반도체 클린룸 전경ⓒ삼성전자

◇SK하이닉스 “테크 플랫폼으로 재사용 늘리고, R&D에도 AI” … 개발 케이던스 방어SK하이닉스는 개발 난이도 급등 국면에서 “기존 방식으로는 ‘개발 케이던스(Cadence, 작업 속도)를 지키기 어렵다”는 문제의식을 전면에 뒀다. 해결책으로 제시한 축은 테크 플랫폼이다. 주요 공정을 모듈화하고, 단위 공정을 2세대·3세대 이상 재사용하도록 설계해 세대 전환 때마다 반복되는 리스크와 지연을 줄이겠다는 접근이다.여기에 R&D 과정에도 AI를 도입하겠다는 계획을 내놨다. 사람과 자원 투입을 늘리는 방식만으로는 개발 기간 단축에 한계가 있고, 축적 데이터와 외부 지식(논문·공개 자료 등)을 활용해 물질 탐색·검증 같은 초기 구간을 줄이겠다는 구상이다.또 협력사와 로드맵을 공유해 소재·장비 개발 방향을 맞추는 방식의 ‘선제 협업’도 강조했다.양사가 “시간”을 말했지만, 성패는 내부 선언보다 실행 구조에 달려 있다. 고적층 HBM은 설계 변경 한 번이 패키징·열·전력·신뢰성 검증의 재작업으로 번질 수 있다. 고객 요구가 상향될수록 재설계·재검증이 반복될 가능성도 변수다.업계 관계자는 "플랫폼 재사용과 공동 최적화가 실제 리드타임으로 연결되려면 소부장 로드맵이 함께 맞아야 한다"면서 "공정·검증 데이터가 다음 세대에 재활용되는 체계(데이터 구조)까지 갖춰져야 ‘개발시간 단축’이 숫자로 증명될 것"이라고 말했다.